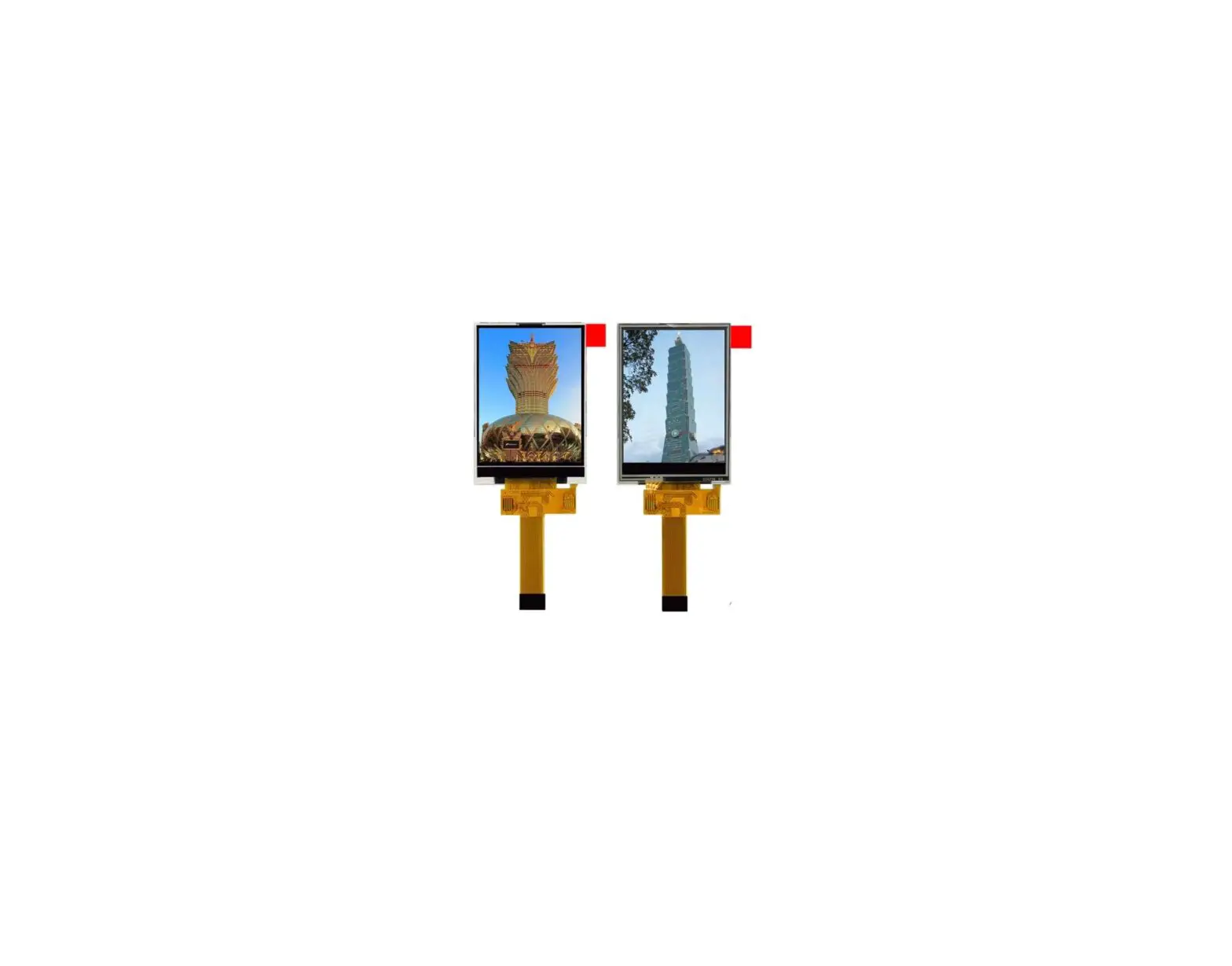

Surenoo STP0240C1-240320 Series TFT LCD Panel

General Description

| MODEL NO | STP0240C1-240320 YT240L002 |

| Display Mode | Transmissive |

| Display Format | Graphic 240RGB*320 Dot-matrix 240xRGBx320 |

| Input Data | MCU-8bit/16bit interface MUC 8 |

| Viewing Direction | 12 o’clock 12 |

| Drive | ILI9341V |

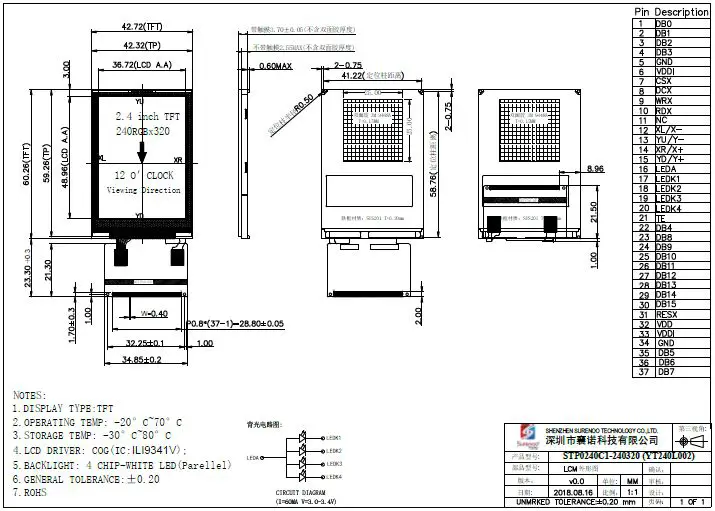

Mechanical Specification

| Item | Specifications | Unit |

| Dimensional outline | 42.72(W)*60.26(H)*2.55(T)(NTP) 42.72(W)*60.26(H)*3.75(T)(RTP) (FPC not include) | mm |

| Resolution | 240RGB*320 | dots |

| LCD Active area | 36.72(W)*48.96 (H) | mm |

| Pixel size | 0.153(W)*0.153(H) | mm |

Mechanical Dimension

Electrical Maximum Ratings

| Item | Symbol | Min | Max | Unit | Note |

| Supply voltage(VDDI) | V | 1.8 | 3.3 | V | – |

| Supply voltage(VDD) | V | 2.8 | 3.3 | V | – |

| Operating temperature 工 | TOPR | –20 | 70 | ℃ | – |

| Storage temperature | TSTR | –30 | 80 | ℃ | – |

NOTE: VDDI VDD(2.8V~3.3V)。

Brightness characteristic&Power dissipation

| Item | Symbol | Min | Typical | Max | Unit |

| LED module Forward voltage | VLED | 2.9 | 3.1 | 3.3 | V |

| LED module current | ILED | – | 60 | – | mA |

| LCD Surface Luminance | LS | 250 | 300 | – | Cd/m2 |

| LCM Surface brightness uniform | LD | 80 | – | – | % |

| LCD power dissipation | PLCD | – | 0.22 | – | W |

NOTE:PLCD=VDD * (ILED+ILCD)

Module Function Description

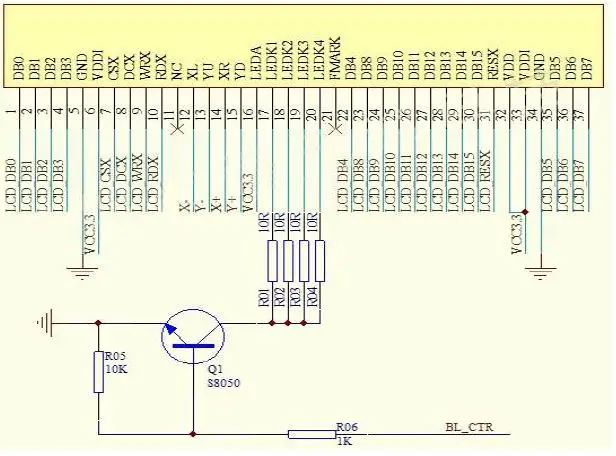

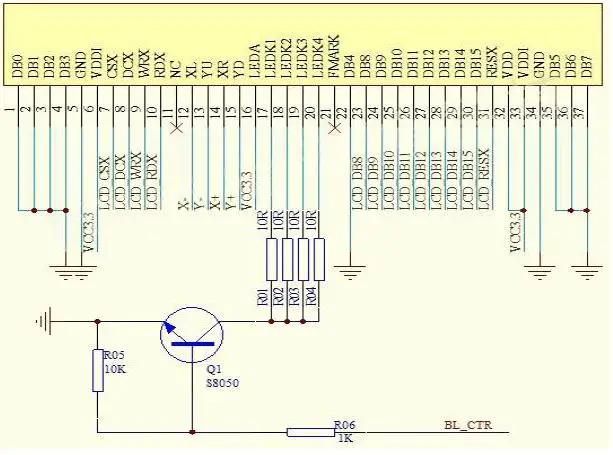

| PIN No. | Symbol | Description | Notes |

| 1-4 | DB0-DB3 | MCU parallel interface data bus. | – |

| 5 | GND | Ground | – |

| 6 | VDDI | Power Supply for I/O System. | – |

|

7 |

CSX | -Chip selection pin Low enable. High disable. |

– |

|

8 |

DCX | -Display data/command selection pin in parallel interface. DCX=’1’: display data or parameter. (DCX=1: DCX=’0’: command data (DCX=0: |

– |

| 9 | WRX | -Write enable in MCU parallel interface. | – |

| 10 | RDX | -Read enable in 8080 MCU parallel interface. -If not used, please fix this pin at VDDI or GND. | – |

| 11 | NC | No connection | – |

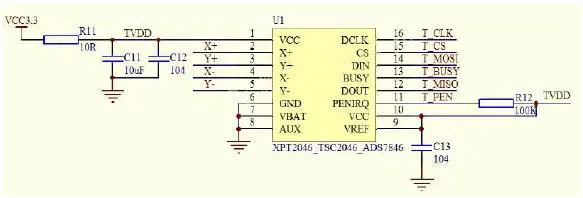

| 12 | XL(X-) | Touch panel Logical foot | – |

| 13 | YU(Y-) | Touch panel Logical foot | – |

| 14 | XR(X+) | Touch panel Logical foot | – |

| 15 | YD(Y+) | Touch panel Logical foot | – |

| 16 | LEDA | Anode of Backlight (2.9V-3.3V Typical:3.1V) | – |

| 17 | LEDK1 | Cathode of Backlight | – |

| 18 | LEDK2 | Cathode of Backlight | – |

| 19 | LEDK3 | Cathode of Backlight | – |

| 20 | LEDK4 | Cathode of Backlight | – |

| 21 | TE | Tearing effect signal is used to synchronize MCU to frame memory | – |

| 22 | DB4 | MCU parallel interface data bus. | – |

| 23-30 | DB8-DB15 | MCU parallel interface data bus. | – |

| 31 | RESX | -This signal will reset the device and it must be applied to properly initialize the chip. -Signal is active low. | – |

| 32 | VDD | Power Supply for Analog, Digital System and Booster Circuit. | – |

| 33 | VDDI | Power Supply for I/O System. | – |

| 34 | GND | Ground | – |

| 35-37 | DB5-DB7 | MCU parallel interface data bus. | – |

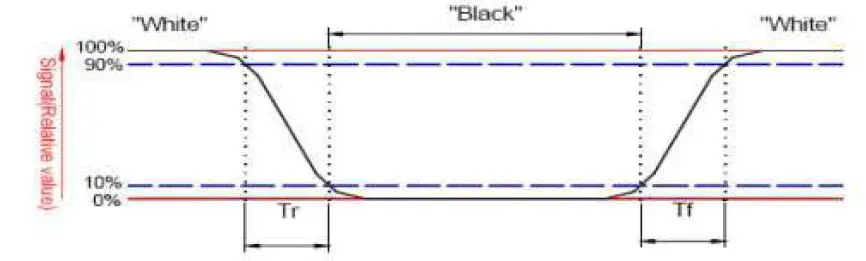

Response time&Contrast ratio

| Item | Symbol | Condition | Remark | Unit | ||

| Min. | Typ. | Max. | ||||

| Response time | Tr+Tf | θ=0° | – | 25 | 40 | ms |

| Contrast ratio | CR | θ=0° | 350 | 500 | – | – |

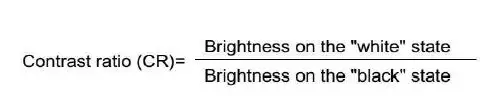

Viewing Angle

| Item | Symbol | Condition | Remark | Unit | ||

| Min. | Typ. | Max. | ||||

|

Viewing angle | Top | CR≥10 | 40 | 50 | – |

Deg. |

| Bottom | CR≥10 | 55 | 65 | – | ||

| Left | CR≥10 | 55 | 65 | – | ||

| Right | CR≥10 | 55 | 65 | – | ||

Reliability Trial

| NO. | ITEM | CONDITION | CRITERION |

| 1 | High Temperature Non-Operating Test | 80℃*120Hrs | No Defect Of |

| Operational | |||

| 2 | Low Temperature Non-Operating Test | -30℃*120Hrs | Function In Room |

| Temperature Are | |||

| 3 | High Temperature/Humidity Non Operating Test | 60℃*90%RH*120Hrs | Allowable |

| 4 | High Temperature Operating Test | 70℃*72Hrs | |

| 5 | Low Temperature Operating Test | -20℃*72Hrs | |

| 6 | Thermal Shock Test | -20 ℃ (30Min) Q70 ℃ | |

| (30Min) *10CYCLES |

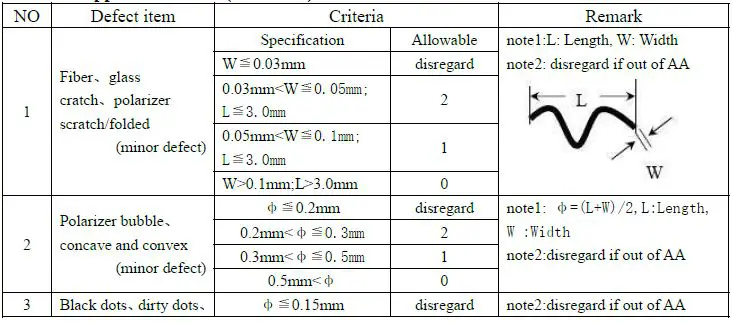

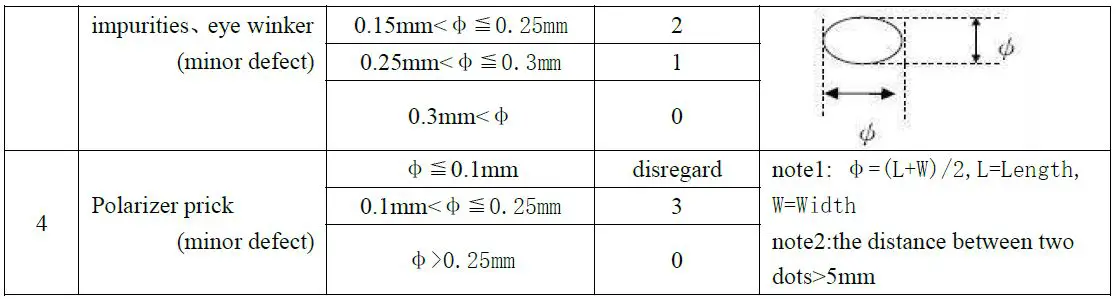

Inspection standards

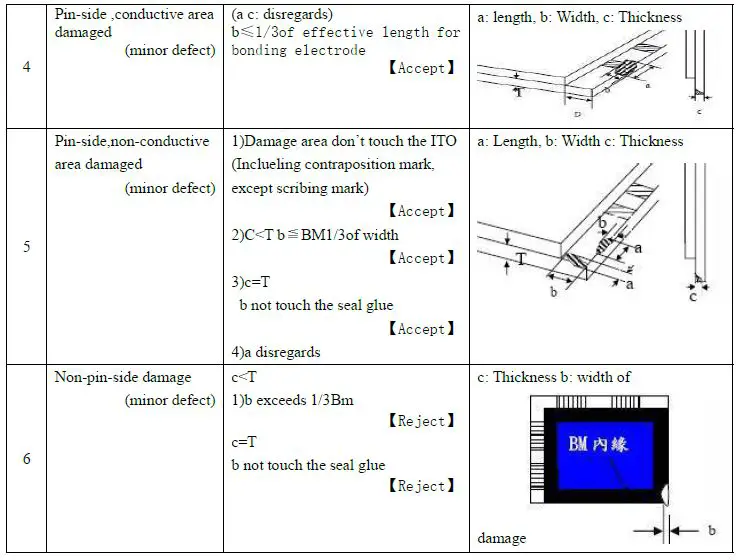

Glass defect

| NO | Defect item | Criteria | Remark |

| 1 | Dimension Unconformity (Major defect) | By Engineering Drawing | |

|

2 | Cracks (Major defect) | 1. Linear cracks panel 【Reject】 2. Nonlinear crack contrast by limited sample |  |

|

3 | Glass extrude the conductive area (minor defect) | a: disregards and no influence assemblage. 1) b≤1/3Pin width(non bonding area) 【Accept】 2)bonding area≤0.5mm 【Accept】 | A: Length, b: Width |

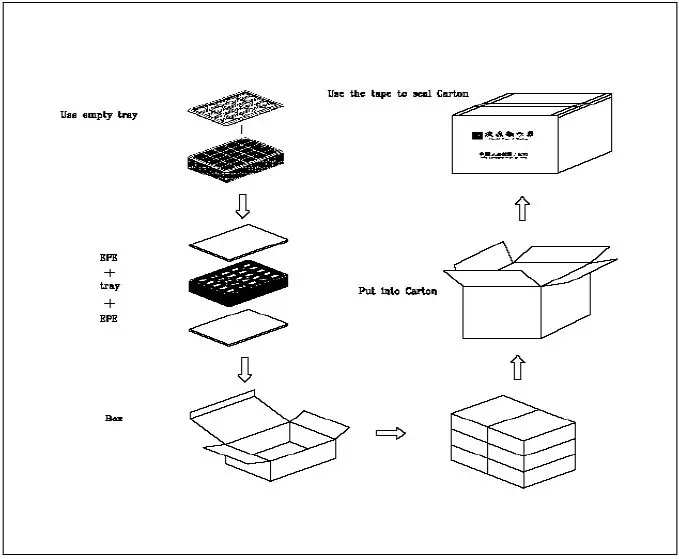

Package Method

Shenzhen Surenoo Technology Co.,Ltd.

www.surenoo.com

Skype: Surenoo365