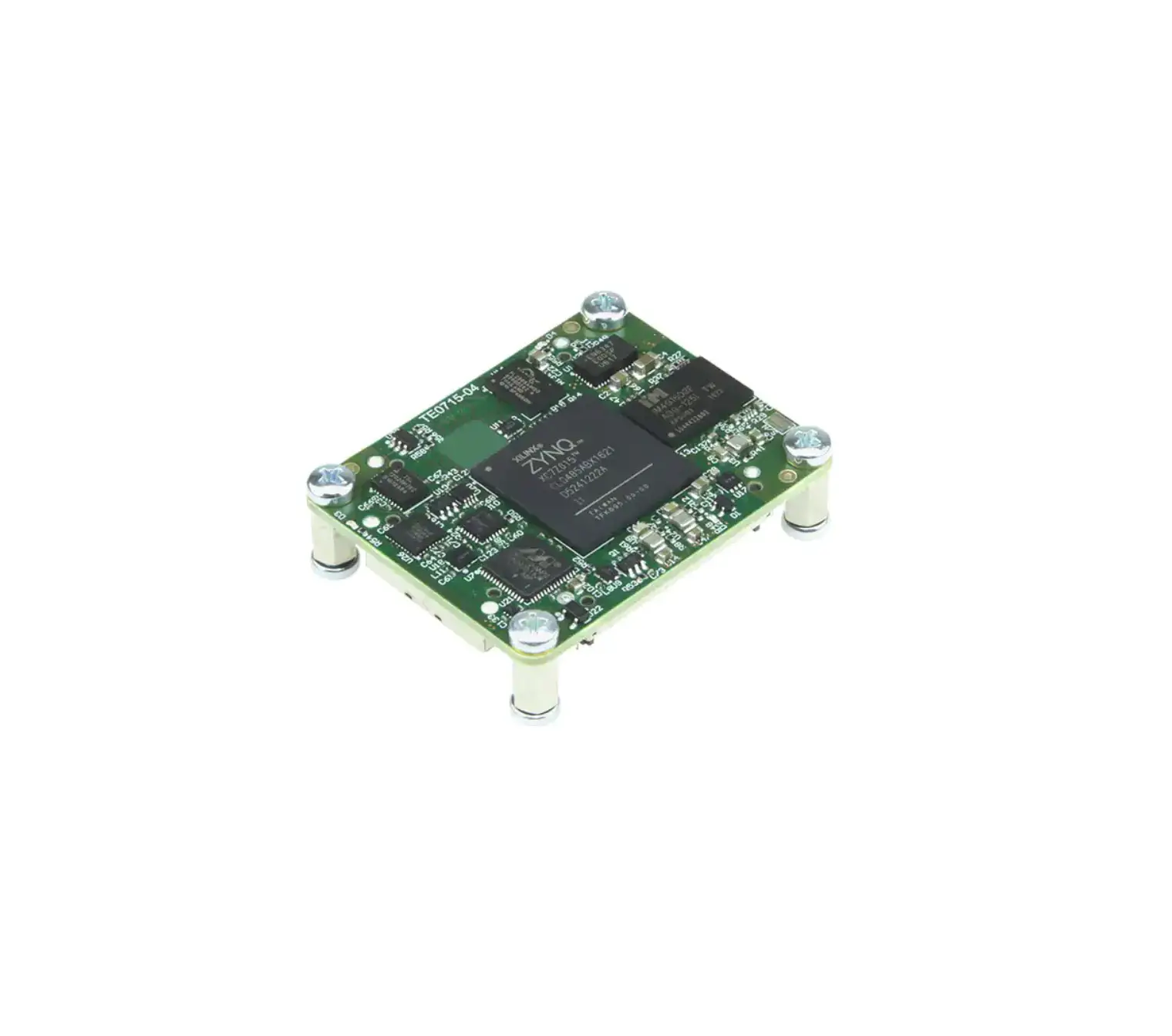

trenz electronic TE0715 CPLD SoC Module Instructions

Overview

Firmware for PCB CPLD with designator U26 : LCMX02-256HC

Feature Summary

- Power Management

- Reset

- CPLD JTAG

- Boot Mode

- PUDC

- ETH

- LED

Firmware Revision and supported PCB Revision

See Document Change History

Product Specification

Port Description

| Name / opt. VHD Name | Direction | Pin | Bank Power | Description |

| / LED | out | 25 | 3.3VIN | Red LED D3 |

| CONFIG | out | 4 | 1.8V | ETH config pin |

| EN1 / EN_SC3 | in | 32 | 3.3VIN | B2B Power Enable |

| JTAGEN | in | 26 | 3.3VIN | JTAG enable for CPLD Firmware update |

| MODE /MODE_SC1 | in | 30 | 3.3VIN | B2B Boot Mode Pin |

| MODE0_R / BOOT_R0 | out | 12 | 3.3V | Zina Boot Mode Pin |

| MODE2_R / BOOT_R2 | out | 17 | 3.3V | Zina Boot Mode Pin |

| MODE3_R / BOOT_R3 | out | 13 | 3.3V | Zina Boot Mode Pin |

| MR / POR_B | out | 10 | 3.3V | Zina Reset |

| N.C. | 8 | 3.3V | / currently_not_used | |

| N.C. | 9 | 3.3V | / currently_not_used | |

| NOSEQ / NOSEQ_SC4 | in | 29 | 3.3VIN | / currently_not_used |

| PG_3V3 / PG_1V5 | in | 28 | 3.3VIN | Power Good |

| PG_DDR_PWR / PG_1V8 | in | 27 | 3.3VIN | Power Good |

| PG_MGT | in | 11 | 3.3V | / currently_not_used |

| PGOOD / STAT_SC2 | out | 1 | 3.3VIN | B2B Power Good |

| PHY_LED1 | in | 5 | 1.8V | PHY LED Pin |

| RESIN / nRST_SC0 | in | 23 | 3.3VIN | B2B Reset |

| SCL33 / SCL | in | 14 | 3.3V | / currently_not_used |

| SDA33 / SDA | input | 16 | 3.3V | / currently_not_used |

| X0 / XA_SC | out | 21 | VCCIO34 | FPGA Pin K8 |

| X1 / XB_SC | out | 20 | VCCIO34 | PUDC FPGA Pin K7 |

Functional Description

JTAG

Power

PGOOD is PG_3V3 and PG_DDR_PWR and EN1

There is no additional power control.

Reset

POR_B is RESIN and PG_3V3 and PG_DDR_PWR and EN1 with some delay.

PUDC

X1 is constant high. Pullups disabled.

Boot Mode

- MODE0_R is constant one.

- MODE2_R is not MODE.

- MODE3_R is constant zero.

| Mode | Boot Mode |

| GND | SD Boot |

| VDD | QSPI Boot |

ETH

CONFIG is constant zero.

PHY_LED1 is connected to X0.

LED

LED is not POR_B.

Appx. A: Change History and Legal Notices

Revision Changes

Document Change History

To get content of older revision got to “Change History” of this page and select older document revision number.

| Date | Document Revision | CPLD Firmware Revision | Supported PCB Revision | Authors | Description |

| 2018-07-17 |

| REV02 | REV04,REV0 3 | @ John Hartfiel |

|

| 2018-07-16 | v.1 | @ John Hartfiel | Initial release | ||

| All | @ Mohsen Chamanbaz, John Hartfiel |

Legal Notices

Data Privacy

Please also note our data protection declaration at https://www.trenz-electronic.de/en/Data-protection-Privacy

Document Warranty

The material contained in this document is provided “as is” and is subject to being changed at any time without notice. Trenz Electronic does not warrant the accuracy and completeness of the materials in this document.

Further, to the maximum extent permitted by applicable law, Trenz Electronic disclaims all warranties, either express or implied, with regard to this document and any information contained herein, including but not limited to the implied warranties of merchantability, fitness for a particular purpose or non infringement of intellectual property. Trenz Electronic shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein.

References

Trenz Electronic GmbH | Entwicklung, Integration, Produktion und Vertrieb von FPGA- und SoC-Modulen | Trenz Electronic GmbH

Trenz Electronic GmbH | Entwicklung, Integration, Produktion und Vertrieb von FPGA- und SoC-Modulen | Trenz Electronic GmbH Confluence Mobile - Trenz Electronic Wiki

Confluence Mobile - Trenz Electronic Wiki Confluence Mobile - Trenz Electronic Wiki

Confluence Mobile - Trenz Electronic Wiki Confluence Mobile - Trenz Electronic Wiki

Confluence Mobile - Trenz Electronic Wiki Confluence Mobile - Trenz Electronic Wiki

Confluence Mobile - Trenz Electronic Wiki Data protection & Privacy | Trenz Electronic GmbH

Data protection & Privacy | Trenz Electronic GmbH