AN706 Simultaneous Sampling Multi-Channels 16-Bits AD Module

8-Channel AD Acquisition Module

AN706 User Manual

Part 1: 8-Channel AD Acquisition Module Parameters

- Module VPN: AN706

- AD Chip: AD7606

- Channel: 8-channel

- AD bits: 16-bit

- Max Sample Rate: 200KSPS

- Input Voltage Rate: -5V~+5V

- PCB layers of Module: 4-Layer independent power layer and GND

layer - Module Interface: 40-pin 0.1 inch spacing female header,

download module to meet the industrial requirements - Input interface: 8 SMA interfaces and 16-pin headers with 2.54

pitch (Pin Each channel has positive and negative two Pin) - Measurement accuracy: Within 0.5mV

Part 2: Module structure

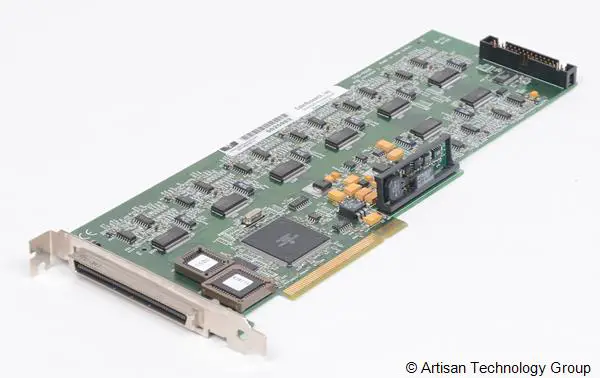

Figure 2-1 shows the structure of the module.

Part 3: AD7606 Chip Introduction

The AD76061 is a 16-bit, simultaneous sampling,

analog-to-digital data acquisition systems (DAS) with eight, six,

and four channels, respectively. Each part contains analog input

clamp protection, a second-order antialiasing filter, a

track-and-hold amplifier, a 16-bit charge redistribution successive

approximation analog-to-digital converter (ADC), a flexible digital

filter, a 2.5 V reference and reference.

The AD7606 has 1 M analog input impedance regardless of sampling

frequency. The single supply operation, on-chip filtering, and high

input impedance eliminate the need for driver op amps and external

bipolar supplies. The AD7606/AD7606-6/AD7606-4 antialiasing filter

has a 3 dB cutoff frequency of 22 kHz and provides 40 dB antialias

rejection when sampling at 200 kSPS. The flexible digital filter is

pin driven, yields improvements in SNR, and reduces the 3 dB

bandwidth.

Part 4: AD7606 Chip Functional Block Diagram

Figure 4-1 shows the functional block diagram of the AD7606

chip.

Part 5: AD7606 Chip Timing Specification

The AD7606 allow simultaneous sampling of all eight analog input

channels. All channels are sampled simultaneously when both CONVST

pins (CONVST A, CONVST B) are tied together. A single CONVST signal

is used to control both CONVST x inputs. The rising edge of this

common CONVST signal initiates simultaneous sampling on all analog

input channels (V1 to V8).

Part 6: AD7606 Chip Pin Configuration

In the AN706 8-channel AD module hardware circuit design, we set

the AD7606’s operating mode by adding pull-up or pull-down

resistors to the three configuration pins of the AD7606.

- The AD7606 supports an external reference input or an internal

reference. If an external reference is used, the REFIN/REFOUT of

the chip requires an external 2.5V reference. If using an internal

reference voltage. The REFIN/REFOUT pin is an internal 2.5V

reference. The REF SELECT pin is used to select the internal

reference or external reference. In this module, because the

accuracy of the internal reference voltage of the AD7606 is also

very high (2.49V~2.505V), the circuit design chooses to use the

internal reference.

Product Usage Instructions

- Connect the 8 SMA interfaces and 16-pin headers with 2.54 pitch

to the input devices that you want to monitor. - Ensure that the input voltage rate is between -5V~+5V.

- Connect the module interface to a power source and download

module to meet the industrial requirements. - Set the AD7606’s operating mode by adding pull-up or pull-down

resistors to the three configuration pins of the AD7606. Choose

either an internal or external reference voltage using the REF

SELECT pin. - Use a single CONVST signal to control both CONVST x inputs. The

rising edge of this common CONVST signal initiates simultaneous

sampling on all analog input channels (V1 to V8). - The collected data can be analyzed using appropriate

software.

8-Channel AD Acquisition Module

AN706 User Manual

8-Channel AD Acquisition Module User Manual

Table of Contents

Part 1: 8-Channel AD Acquisition Module Parameters……………………………… 3 Part 2: Module structure…………………………………………………………………………… 3 Part 3: AD7606 Chip Introduction………………………………………………………………4 Part 4: AD7606 Chip Functional Block Diagram……………………………………….. 5 Part 5: AD7606 Chip Timing Specification………………………………………………… 6 Part 6: AD7606 Chip Pin Configuration……………………………………………………..7 Part 7: AD7606 Chip ADC TRANSFER FUNCTION…………………………………. 8 Part 8: Interface definition (The labeled pin on the PCB is pin 1)……………… 9 Part 9: AN706 Module Experimental procedure……………………………………… 10 Part 10: AN706 Module Measurement Accuracy……………………………………..13 Part 11: AN706 Module test program description…………………………………….13

2/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

Part 1: 8-Channel AD Acquisition Module Parameters

Module VPN: AN706 AD Chip: AD7606 Channel: 8-channel AD bits: 16-bit Max Sample Rate: 200KSPS Input Voltage Rate: -5V~+5V PCB layers of Module: 4-Layerindependent power layer and GND

layer Module Interface: 40-pin 0.1 inch spacing female header, download

direction Ambient Temperature (with power applied: -40°~85°, all the chips on

module to meet the industrial requirements Input interface: 8 SMA interfaces and 16-pin headers with 2.54 pitch

(Pin Each channel has positive and negative two Pin) Measurement accuracy: Within 0.5mV

Part 2: Module structure

3/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

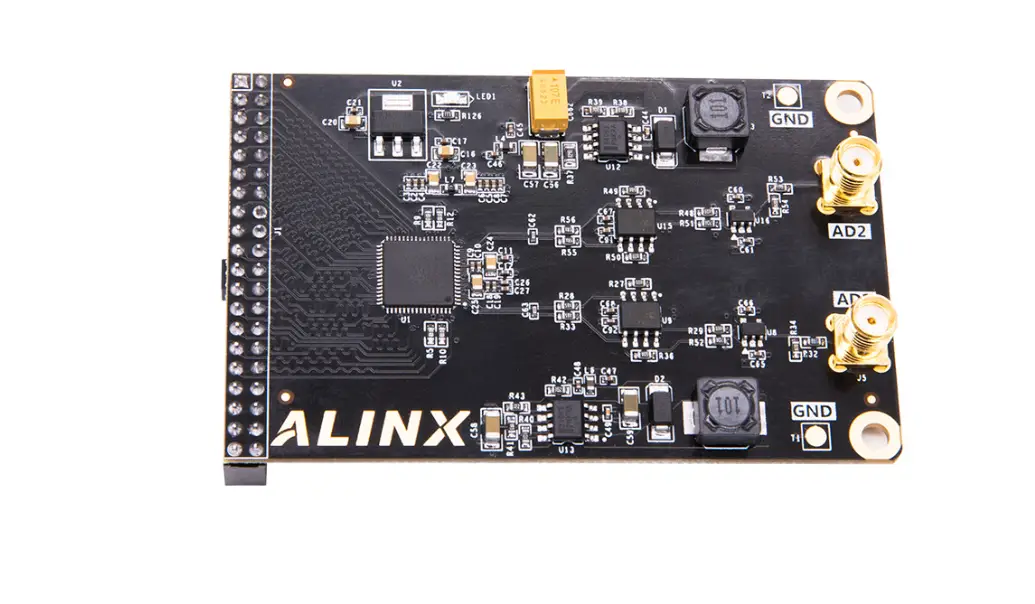

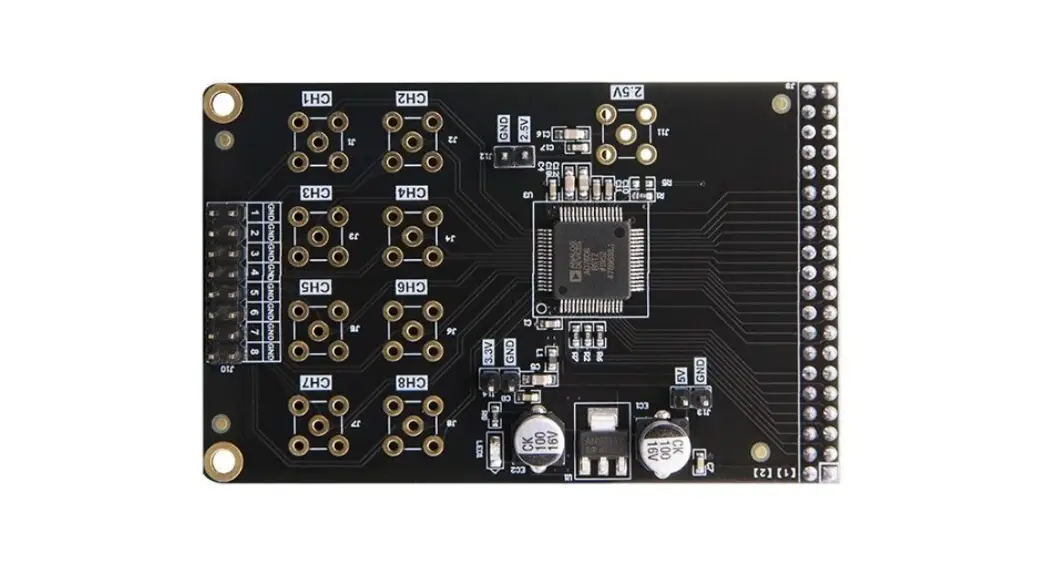

Figure 2-1: The 8-channel AD module structure

Part 3: AD7606 Chip Introduction

The AD76061 is 16-bit, simultaneous sampling, analog-to-digital data acquisition systems (DAS) with eight, six, and four channels, respectively. Each part contains analog input clamp protection, a second-order antialiasing filter, a track-and-hold amplifier, a 16-bit charge redistribution successive approximation analog-to-digital converter (ADC), a flexible digital filter, a 2.5 V reference and reference

The input clamp protection circuitry can tolerate voltages up to ±16.5 V. The AD7606/AD7606-6/AD7606-4 operate from a single 5 V supply and can accommodate ±10 V and ±5 V true bipolar input signals while sampling at throughput rates up to 200 kSPS for all channels. The input clamp protection circuitry can tolerate voltages up to ±16.5 V.

The AD7606 has 1 M analog input impedance regardless of sampling frequency. The single supply operation, on-chip filtering, and high input

4/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

impedance eliminate the need for driver op amps and external bipolar supplies. The AD7606/AD7606-6/AD7606-4 antialiasing filter has a 3 dB cutoff frequency of 22 kHz and provides 40 dB antialias rejection when sampling at 200 kSPS. The flexible digital filter is pin driven, yields improvements in SNR, and reduces the 3 dB bandwidth.

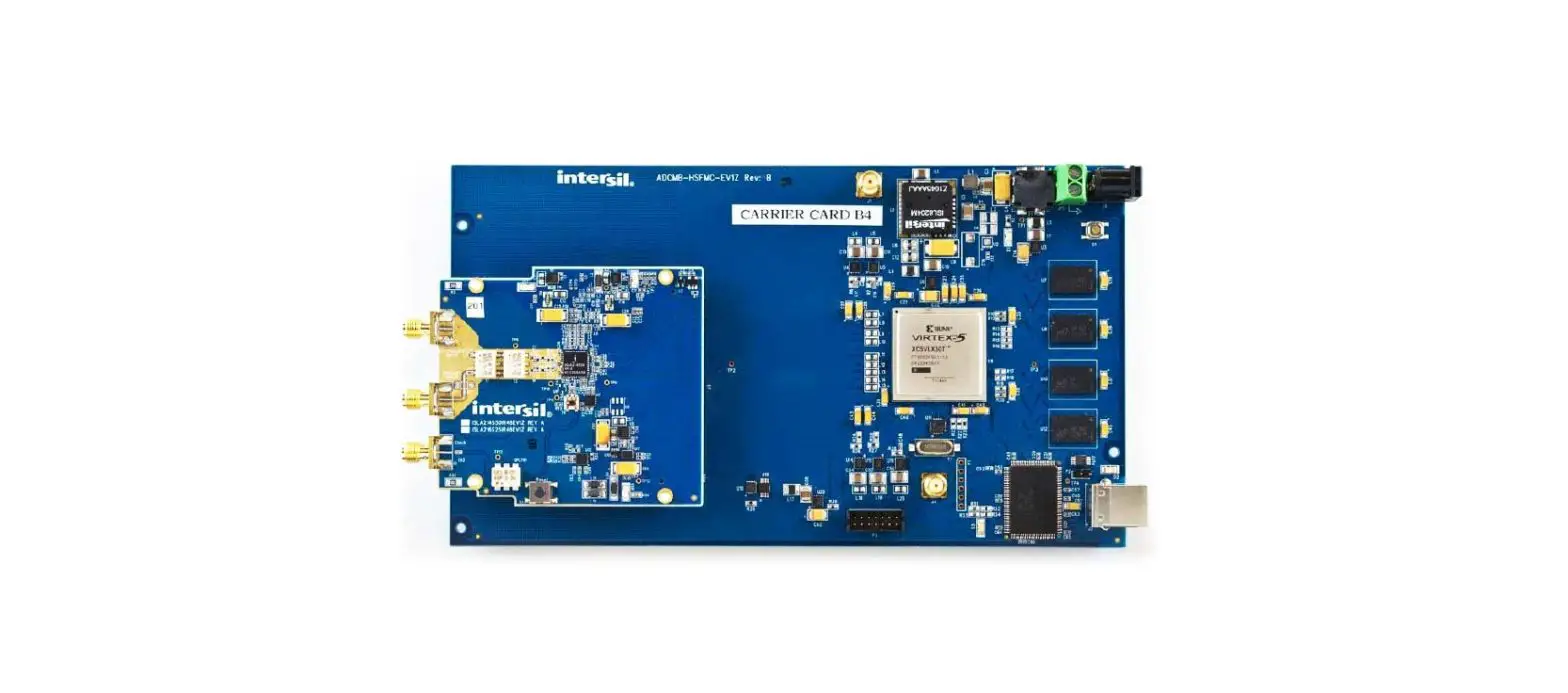

Part 4: AD7606 Chip Functional Block Diagram

Figure 4-1: AD7606 Functional Block Diagram

5/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

Part 5: AD7606 Chip Timing Specification

Figure5-1: AD7606 Timing Diagrams

The AD7606 allow simultaneous sampling of all eight analog input channels. All channels are sampled simul-taneously when both CONVST pins (CONVST A, CONVST B) are tied together. A single CONVST signal is used to control both CONVST x inputs. The rising edge of this common CONVST signal initiates simultaneous sampling on all analog input channels (V1 to V8).

The AD7606 contains an on-chip oscillator that is used to perform the conversions. The conversion time for all ADC channels is t . CONV The BUSY signal indicates to the user when conversions are in progress, so when the rising edge of CONVST is applied, BUSY goes logic high and transitions low at the end of the entire conversion process. The falling edge of the BUSY signal is used to place all eight track-and-hold amplifiers back into track mode. The falling edge of BUSY also indicates that the new data can now be read from the parallel bus (DB[15:0]), the DOUTA and DOUTB serial data lines, or the parallel byte bus, DB[7:0].

6/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

Part 6: AD7606 Chip Pin Configuration

In the AN706 8-channel AD module hardware circuit design, we set the

AD7606’s operating mode by adding pull-up or pull-down resistors to the three

configuration pins of the AD7606.

1. The AD7606 supports an external reference input or an internal

reference. If an external reference is used, the REFIN/REFOUT of

the chip requires an external 2.5V reference. If using an internal

reference voltage. The REFIN/REFOUT pin is an internal 2.5V

reference. The REF SELECT pin is used to select the internal

reference or external reference. In this module, because the

accuracy of the internal reference voltage of the AD7606 is also

very high (2.49V~2.505V), the circuit design chooses to use the

internal reference voltage.

Pin Name

Set level

Description

REF SELECT High Level

Use internal reference voltage 2.5V

2. The AD7606’s AD conversion data acquisition can be in parallel

mode or serial mode. The user can set the communication mode by

setting the PAR/SER/BYTE SEL pin level. in the AN706 module

design, select parallel mode to read AD data of AD7606

Pin Name

Set level

Description

PAR/SER/BYTE SEL Low Level Select parallel interface

3. The RANGE pin is used to select either ±10 V or ±5 V as the input range in AD9767. In the ±5 V range, 1LSB=152.58uV. In the ±10 V range, 1LSB=305.175 uV. In the circuit design of AN706 module, select ±5V analog voltage input range

7/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

Pin Name RANGE

Set level Low Level

Description Analog signal input range selection±5V

4. The AD7606 contains an optional digital first-order sinc filter that should be used in applications where slower throughput rates are used or where higher signal-to-noise ratio or dynamic range is desirable. The oversampling ratio of the digital filter is controlled using the oversampling pins, OS [2:0] (see Table below). OS 2 is the MSB control bit, and OS 0 is the LSB control bit. Table below provides the oversampling bit decoding to select the different oversample rates. The OS pins are latched on the falling edge of BUSY.

In the hardware design of the AN706 module, OS[2:0] leads to the external interface, and the FPGA or CPU can select whether to use the filter by controlling the pin level of OS[2:0] to achieve higher measurement accuracy.

Part 7: AD7606 Chip ADC TRANSFER FUNCTION

The output coding of the AD7606 is two’s complement. The designed code transitions occur midway between successive integer LSB values, that is, 1/2 LSB and 3/2 LSB. The LSB size is FSR/65,536 for the AD7606. The ideal transfer characteristic for the AD7606 is shown in Figure 7-1.

8/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

Figure 7-1: AD7606 Transfer Characteristics

Part 8: Interface definition (The labeled pin on the PCB is pin 1)

Pin

Signal Name

Description

Pin Signal Name Description

1

GND

Ground

2

Oversampling

3

OS1

4

Select

5

CONVSTAB Data conversion

6

7

RD

Read

8

VCC OS0 OS2 RESET

+5V Oversampling

Select Oversampling

Select Reset

9

BUSY

Busy

10

CS

Chip Select

9/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

11

12

FIRSTDATA

First data

13

14

15

DB0

AD Data Bus

16

DB1

AD Data Bus

17

DB2

AD Data Bus

18

DB3

AD Data Bus

19

DB4

AD Data Bus

20

DB5

AD Data Bus

21

DB6

AD Data Bus

22

DB7

AD Data Bus

23

DB8

AD Data Bus

24

DB9

AD Data Bus

25

DB10

AD Data Bus

26

DB11

AD Data Bus

Part 9: AN706 Module Experimental procedure

1) First, connect the AN706 module to the 34-pin standard expansion port of the ALINX FPGA Development Board (In case the development board is powered off).

2) Connect your signal source to the AN706 Module input connector (Note: AD port input range: -5V~+5V).

3) Download the program to the FPGA using the Quartus II or ISE software (if you need the testing programs, send email to [email protected]).

4) Open the serial debugging assistant tool and set the communication baud rate of the serial port as follows

10/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

Figure 9-1: The Serial Debugging Assistant Tool

5) The voltage value of the 8-channel signal input of the AN706 module will appear in the serial communication. (Because the 8-way data is displayed in one line in the serial debugging assistant, we need to enlarge the interface.)

11/14

Figure 9-2: Serial Communication

www.alinx.com

8-Channel AD Acquisition Module User Manual

The above data is 8 channels of data without signal input, because the AD signal input is in a floating state, and the AD conversion output data is about 1.75V.

Example: If you connect the input of channel 1 with the 3.3V test pin on the AN706 module with a DuPont line to test the voltage of 3.3V on the module.

Figure 9-3: Channel 1 with 3.3V test pin

At this time, the measurement data of AD1 displayed on the serial interface is about +3.3074.

Figure 9-4: Test pin voltage display on the serial interface

12/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

Part 10: AN706 Module Measurement Accuracy

By measuring the applied voltage and the high-precision voltmeter, the actual measurement accuracy of the AD706 module is within 0.5mV within the -5V to +5V voltage input range.

The following table shows the results of eight channels for four analog voltages. The first column is the data measured by the high-precision digital multimeter, and the last eight columns are the results of the AD module’s AD module measurement.

Table 10-1: Testing Voltage

In this test routine, the oversampling override enable filter is not used to improve the accuracy of the AN706 module. For users who want to further improve the accuracy of sampling and the sampling speed is not high, it can be set in the program. Method of sampling magnification, you can set the oversampling ratio in the program.

Part 11: AN706 Module test program description

The following is a brief description of the ideas for each Verilog test programs, and users can also refer to the note description in the code.

1. Top level program: ad706_test.v Define the FPGA and AN706 modules and the serial port to receive and send the signal input and output, and instantiate three subroutines (ad7606.v, volt_cal.v and uart.v).

2. AD data acquisition program: ad7606.v

13/14

www.alinx.com

8-Channel AD Acquisition Module User Manual

According to the timing of the AD7606, sample 16 analog signals AD converted 16-bit data. The program first sends the CONVSTAB signal to the AD7606 to start AD data conversion, and waits for the Busy signal to go low to read the data of AD channel 1 to channel 16 in sequence. AD Voltage Conversion (1 LSB)=5V/ 32758=0.15 mV

3. Voltage conversion program for AD data: volt_cal.v The program converts the 16-bit data collected from ad7606.v, Bit[15] into positive and negative signs, and Bit[14:0] first converts it into a voltage value by the following formula, and then converts the hexadecimal voltage value into 20-digit BCD code.

4. Serial port sending program: uart.v Timing sends 8 channels of voltage data to the PC through uart. The serial port’s transmit clock is obtained by dividing the frequency by 50Mhz, and the baud rate is 9600bps.

14/14

www.alinx.com